Samsung a annoncé la production d'une nouvelle puce de génération "3 nanomètres" qui sera bientôt utilisée dans les smartphones et les ordinateurs. Au-delà de la taille, c'est la forme du transistor qui change en fait en mobilisant des nanofeuilles pour transporter le courant.

Samsunga utiliséplus que ses concurrents dans la compétition en cours pour la miniaturisation des processeurs. L'électroménager sud-coréen a annoncé le 30 juin 2022 qu'il dépasserait deux rivaux participant à la compétition, Intel aux États-Unis et TSMC à Taïwan, pour démarrer la production de puces de nouvelle génération.

L'annonce de Samsung porte sur la production de puces avec des détails de gravure allant jusqu'à 3 nanomètres. À cette échelle, l'épaisseur des cheveux semble énorme. Les nanomètres sont une petite partie d'un mètre (un milliardième) et les cheveux sont 50 000 fois plus épais. Aujourd'hui, les puces les plus avancées du marché sont annoncées à 5 et 7 nanomètres (nm).

1/50 000ème d'épaisseur de poil

Les géants asiatiques ne taisent pas d'éloges pour expliquer la qualité de leurs sauts en hausse. Par rapport à 5 nm, ce premier processus de 3 nm "réduit la consommation d'énergie jusqu'à 45 %, améliore les performances de 23 % et réduit la surface de 16 %". De plus, dans le processus de deuxième génération, les gains sont respectivement de 50 %, 30 % et 35 %.

Les progrès constants de l'ingénierie informatique avancée ont pour effet de repousser les déclarations précédentes sur ce sujet à une année-lumière de nous. S'il vous plaît rappelez-vous. En 2017,IBM était fier de pouvoir graver des puces d'une finesse de 5 nmCinq ans plus tard, ce niveau de gravure est devenu assez banal.

Ainsi, la sophistication de cette sculpture est Apple (M1, M2, A14 Bionic, A15 Bionic, etc.), Qualcomm (Snapdragon), Samsung (Exynos), HiSilicon (Kirin), Nvidia (Grace Hopper) . ) Peut être vu. , AMD ou MediaTek aussi. Aujourd'hui, les smartphones et les ordinateurs sont couramment équipés de composants qui bénéficient des avancées dont IBM s'est félicité.

Le calendrier de déploiement de cette nouvelle classe de microprocesseurs n'est pas détaillé dans l'annonce de Samsung, mais ce basculement aura probablement lieu en 2023. Lorsqu'il s'agit d'atteindre une production de masse à vitesse industrielle pour alimenter une chaîne de production qui assemble les futurs composants d'ordinateurs et de smartphones.

Peaufiner la forme du transistor

Il faut noter que le degré de miniaturisation est devenu extrême etles diverses annonces ne justifient pas les progrès de. Fabriqué ces dernières années. Non seulement des termes comme 3 nm, 5 nm, 7 nm, mais aussi certains des seuils ci-dessus font référence à une technologie particulière et à une géométrie particulière de la conception, pas à la taille.

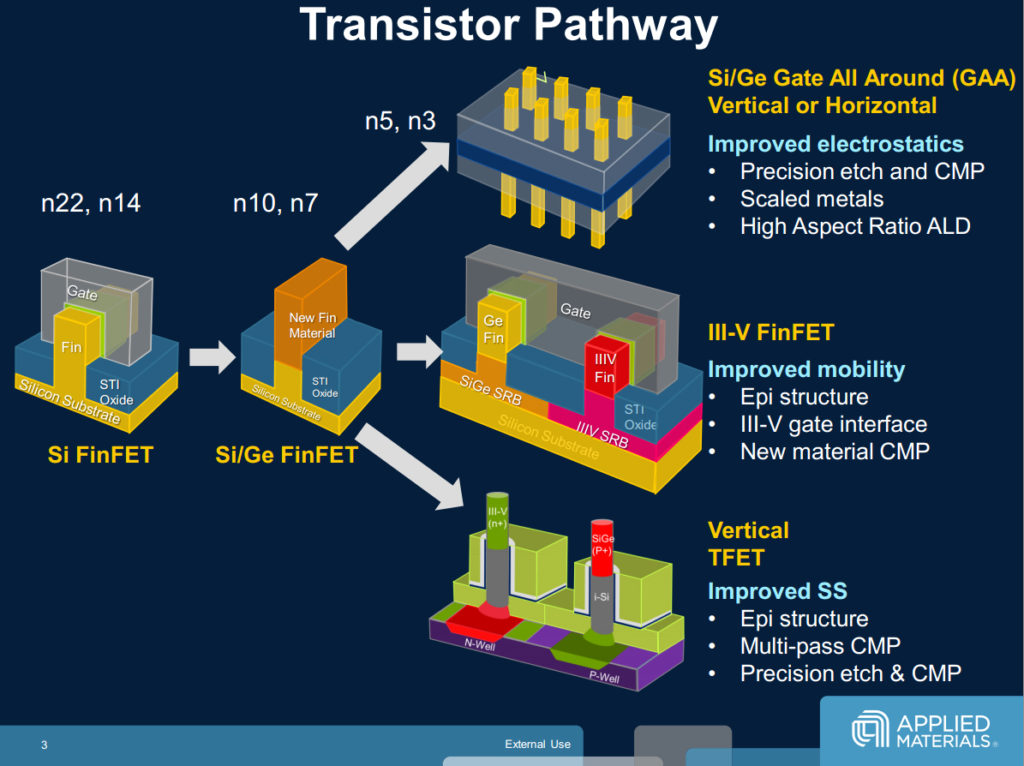

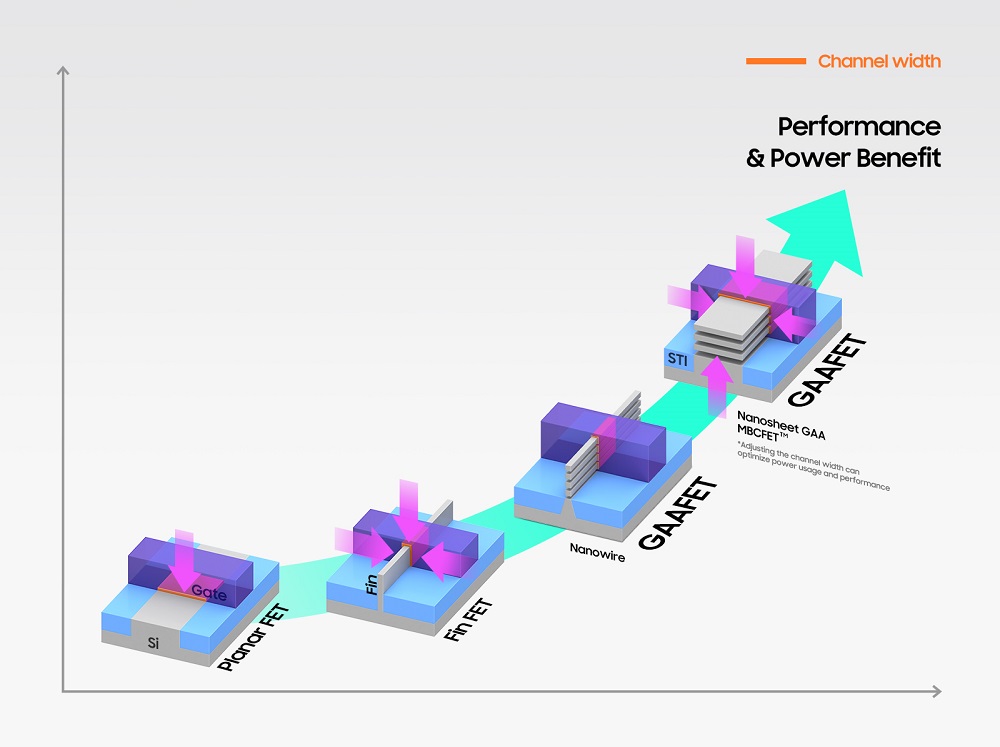

Par conséquent, Samsung s'appuie sur une technique appelée "GAAFET" et une solution maison appelée "MBCFET". Ces acronymes sont ambigus pour ceux qui ne suivent pas strictement l'actualité CPU. A noter qu'à partir des années 2010, les processeurs « 3D » ont commencé à émerger, par opposition à la technologie « plate » traditionnelle.

Ainsi, le secteur a commencé à évoluer vers la solutionFinFET. Ce processus de transformation de la forme du transistor a été utilisé pour générer 14 nm, 10 nm et 7 nm. Vient ensuite la méthode « GAAFET » (gate all-around) qui passe sous le seuil de 7 nm, notamment 5 nm.

GAAFET est un dérivé de FinFET, mais d'une manière ou d'une autre, il s'applique partout. Par conséquent, le portailest nommé autour depour signaler l'existence de certaines portes pour faire passer le courant du transistor. Mais la difficulté est que tout devient très petit et que les électrons fuient. Par conséquent, travaillez maintenant sur la forme du transistor, pas sur la taille du transistor.

Les GAAFET réduisent les canaux de conduction aux nanofils.Les détails seront communiqués en 2019Olivier Faynot, chef de service du Commissariat à l'énergie atomique (CEA) de l'Institut des technologies de l'information électronique. Samsung a développé le "MBCFET" (Multi-Bridge Channel FET) en adoptant la logique derrière le processus "GAAFET".

Nanosheets au lieu de nanofils Samsung

Nous sommes fiers de notre fondeur en Corée car nous avons réussi et dépassé les limites de performance de FinFET en termes d'efficacité énergétique et de performance. Secret. Les nanofils ont été remplacés par des nanofeuilles qui conduisent encore mieux l'électricité. Samsung souligne qu'il s'agit d'une technologie unique.

Ici, des nanofeuilles avec des canaux plus grands sont implémentées pour atteindre les performances mentionnées ci-dessus. Les nanofils et leurs canaux étroits ont été remplacés, et la fonderie prévient que la largeur des canaux peut également être ajustée pour optimiser la consommation d'énergie et les performances afin de répondre aux différents besoins des clients.

Recherche de Samsungque la concurrence pour la miniaturisation se heurte à des obstacles techniques, et que les fabricants adoptent une approche unique pour poursuivre les mises à niveau des processeurs." Un bon exemple de ce que vous êtes obligé de concevoir. Les FinFET, les GAAFET et les MBCFET en sont les démonstrations les plus impressionnantes, et Olivier Faynot ont dit la même chose.

"Le terme utilisé ne correspond pas forcément aux dimensions mesurées dans le circuit intégré. Historiquement, lorsqu'on parle du noeud 28 nm, cette valeur est une grandeur physique. C'est-à-dire qu'il reflétait la longueur de la grille du transistor. Désormais, lorsqu'un homme d'affaires mentionnera un nœud de 5 ou 7 nm, les dimensions seront de l'ordre de 10 nm. "

"Il est largement reconnu dans l'industrie que la nomenclature à l'échelle nanométrique est incohérente et déroutante et ne reflète pas les dernières innovations en matière de transistors",a également déclaré Chelsea Hughes. .. Porte-parole d'IntelCependant, il peut être difficile de quitter le marketing car le groupea évoqué un passage à "ageangström". C'est-à-dire moins de nanomètres.